Sylvain Lefebvre

@sylefeb

Followers

5K

Following

6K

Media

691

Statuses

3K

Researcher-maker-hacker focusing on Computer Graphics with a #retro, #fpga gaming twist. Enjoys #3dprinting and #electronics. Created @iceslapp and #Silice.

France

Joined September 2010

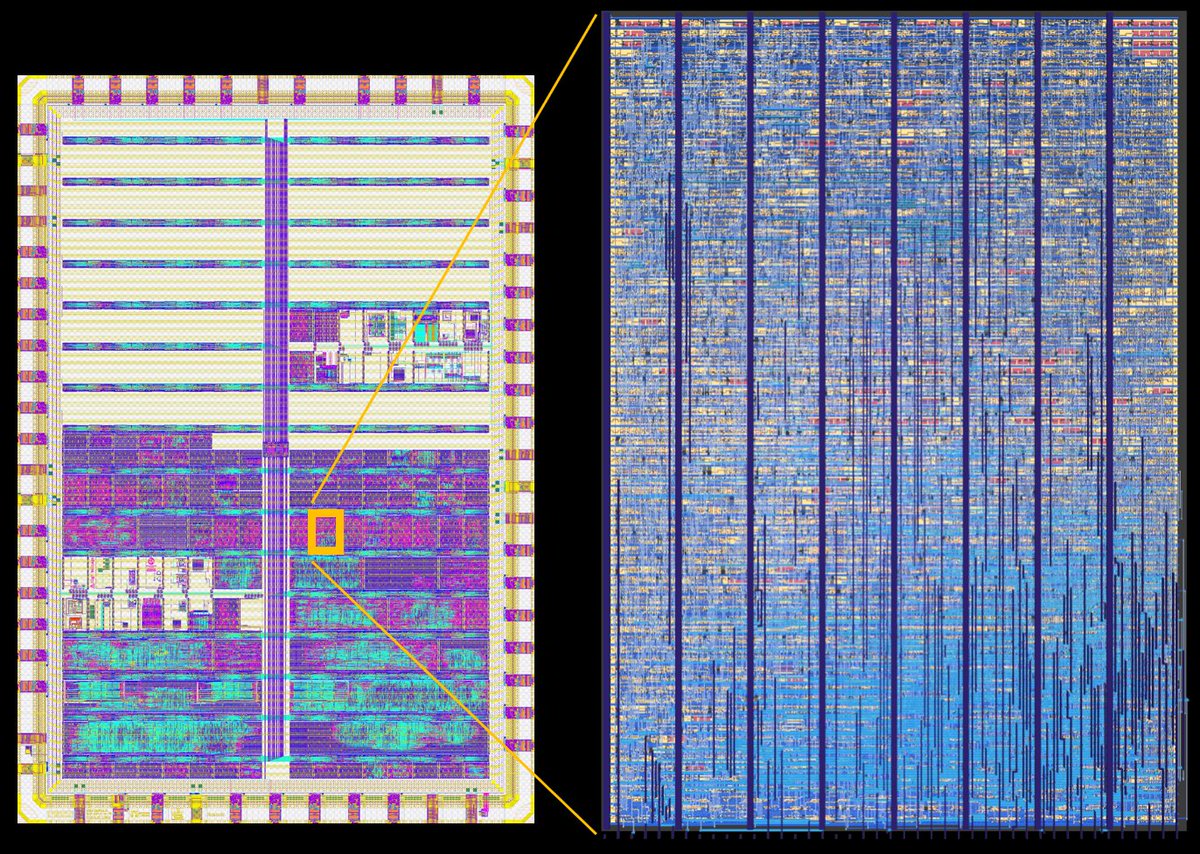

1/ @tinytapeout 7 just closed and these two tiles host my design! If it works, it will generate explorable terrain 'voxels' similar to the VoxelSpace Comanche 1992 game engine.

3

22

146

RT @passivestar_: The new Gabor noise in Blender 4.3 looks really promising for quickly creating some sick stylized shapes ✨ .

0

267

0

RT @exppad: Want to use #WebGPU together with #SDL3?. After recently upgrading #sdl2webgpu, I introduce #sdl3webgpu, little SDL3 extension….

github.com

An extension for the SDL3 library for using WebGPU native. - GitHub - eliemichel/sdl3webgpu: An extension for the SDL3 library for using WebGPU native.

0

5

0

RT @WillFlux: Beginning FPGA Graphics now covers @RadionaOrg #ULX3S (ECP5) in addition to the @DigilentInc Arty / Nexys Video and iCEBreake….

projectf.io

Welcome to Exploring FPGA Graphics. In this series, we learn about graphics at the hardware level and get a feel for the power of FPGAs. We’ll learn how screens work, play Pong, create starfields and...

0

28

0

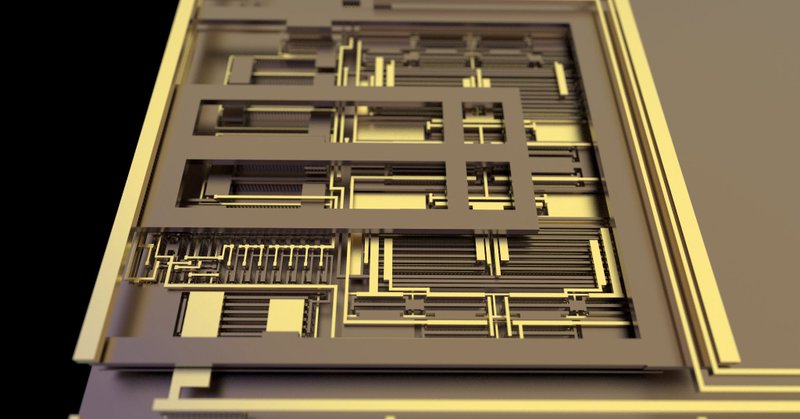

RT @duke_cpu: It’s a #COMET! ☄️ .The #digital DEC705 is a gate array made in the late 1980s. Enjoy the awesome microstructure! https://t.co….

0

19

0

RT @matthewvenn: In case you missed it, @tinytapeout now supports analog and mixed signal!.

zerotoasiccourse.com

Tiny Tapeout 6 marked a significant milestone by introducing support for analog and mixed-signal ASIC designs. This innovation opened up a world of possibilities for open-source chip development,...

0

15

0

RT @xavierchermain: ✨ Real-time rendering of anisotropic specular materials with image-based lighting is challenging due to the complexity….

0

73

0

RT @jangray: #FPGA 1st Soft RISC-V Systems Workshop:.Thu Nov. 7 & Fri Nov. 8, 8am-12pm PDT, the @risc_v Soft CPU SIG is hosting a free onli….

sites.google.com

0

26

0

2/ I followed the @tinytapeout approach of doing the entire synthesis in github actions, with #Silice seamlessly integrated in the mix. Write your code, commit+push, and get back an ASIC design ready to submit to Tiny Tapeout !.

0

0

1

1/ If you feel adventurous and want to try both @tinytapeout (make your own chip!) and #Silice I prepared a template for tt09 (61 days to go!). Be warned: I am waiting for my tt07 and tt08 designs to come back to realize my mistakes 😅.

github.com

Submission template for Tiny Tapeout 9 - Verilog HDL Projects - Silice - sylefeb/tt09-silice-template

1

2

12

RT @WillFlux: I've created a series on RISC-V assembler for software developers. The first part introduces #RISCV, then looks at load immed….

projectf.io

This series will help you learn and understand 32-bit RISC-V instructions and programming. The first part looks at load immediate, addition, and subtraction. We’ll also cover sign extension and...

0

12

0

RT @nand2mario: The first version of GBA core for Tang FPGA is ready 🚀🚀. It's early stage - only some games are working, no save-to-sdcard….

0

21

0

RT @MittringMartin: NVIDIA’s Tech: Finally, Real Time Ray Tracing! (Episode 900 Special!) via @YouTube.

0

12

0