Luffca

@luffca_inc

Followers

1

Following

1

Media

13

Statuses

30

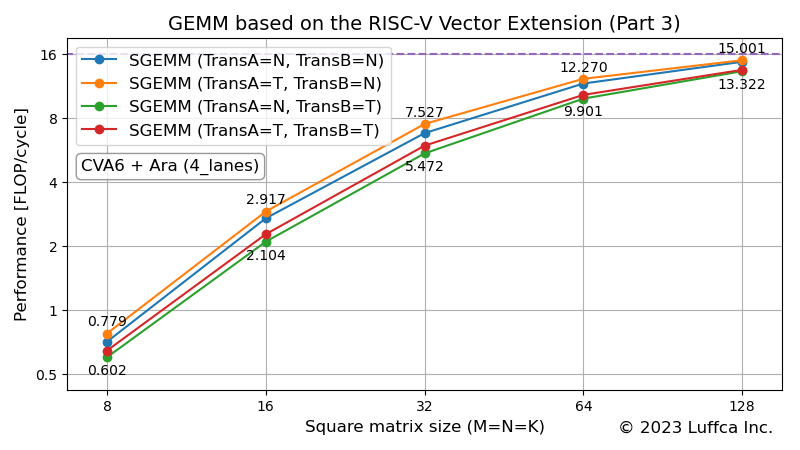

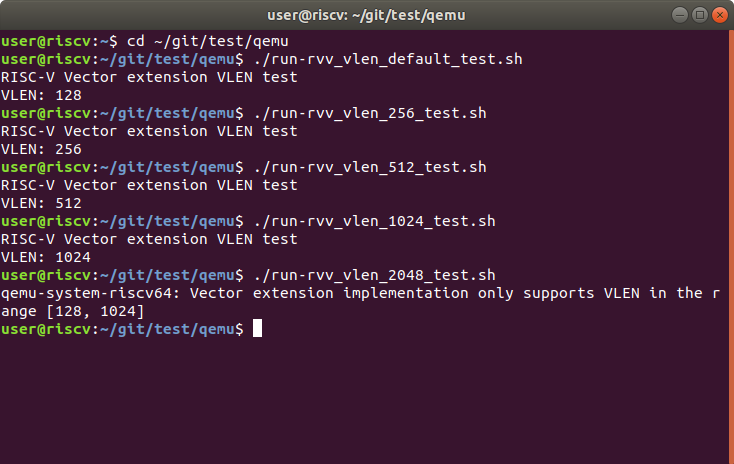

We have posted an article "GEMM based on the RISC-V Vector Extension (Part 3)" which evaluated a GEMM-compatible floating-point matrix multiplication performance.

0

0

0

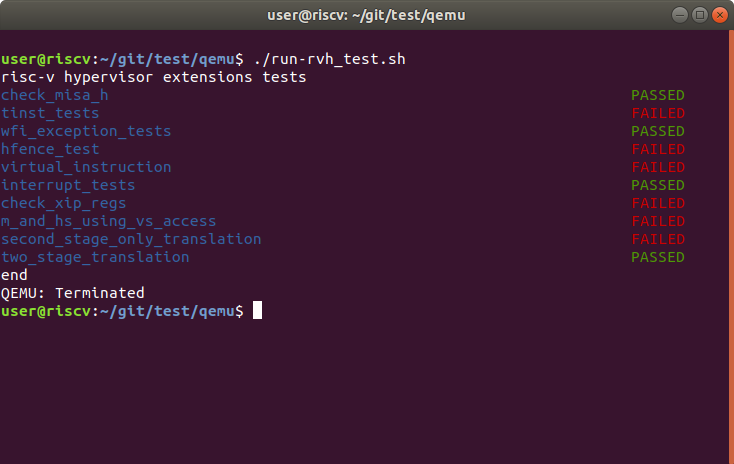

In "CVA6 RISC-V Virtualization: Architecture, Microarchitecture, and Design Space Exploration", researchers add the RISC-V Hypervisor extension to CVA6.

arxiv.org

Virtualization is a key technology used in a wide range of applications, from cloud computing to embedded systems. Over the last few years, mainstream computer architectures were extended with...

0

0

0

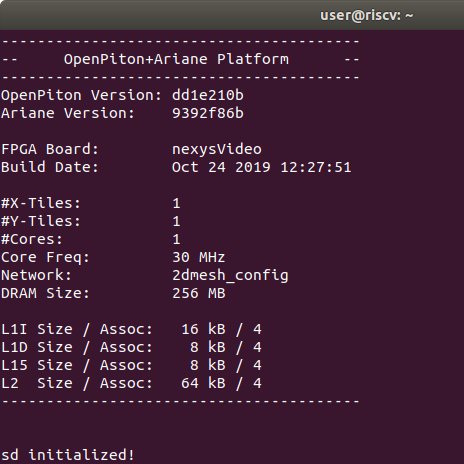

We made OpenBLAS compatible with 32-bit RISC-V and evaluated the performance of GEMM (GEneral Matrix-to-matrix Multiply) on the Nexys Video FPGA board with octa-core VexRiscv SoC.

luffca.com

We made OpenBLAS compatible with 32-bit RISC-V and evaluated the performance of GEMM using an FPGA board with octa-core 32-bit RISC-V SoC.

0

0

0

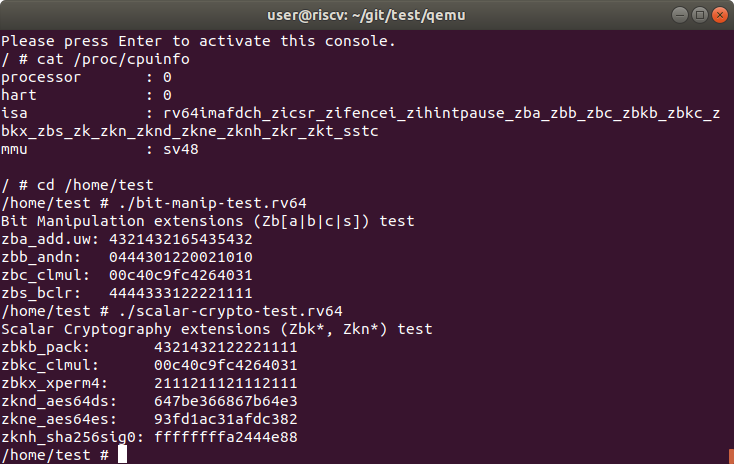

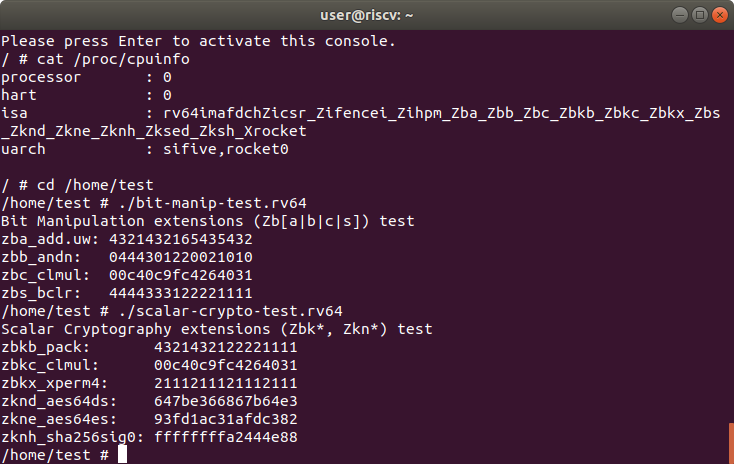

We ran simple tests of Bit Manipulation extensions (Zb[a|b|c|s]) and Scalar Cryptography extensions (Zbk*, Zkn*) on RISC-V SoC with Rocket Chip and LiteX. #RISCV #RocketChip #LiteX

0

0

1