Andrew Elbert Wilson

@FPGA_Zealot

Followers

2K

Following

6K

Media

173

Statuses

747

Joined July 2016

Another Agilex 5 Live Stream this Friday!.We’re diving deeper into the FPGA AI Suite on Agilex 5—how the DLA software uses CSRs to run AI model inference. Huge thanks to @AlteraFPGA_ for the support—come hang out!.

0

0

4

Here is a Python notebook using Cocotb to demo the Agilex 5 FPGA with AI‑optimized DSP in Tensor Mode!.It runs a Sobel top + right edge filter fully pipelined in a single DSP. You can tweak the coefficients and try your own computations. 🔗

github.com

Examples for Altera FPGAs. Contribute to AEW2015/altera_examples development by creating an account on GitHub.

2

6

54

Going live Friday with a demo on the Altera FPGA AI Suite + Agilex 5! We’ll compile ONNX models, show off the new DSPs, and demo on-board edge AI. Huge thanks to @AlteraFPGA_ for supporting this stream—come hang out!. #FPGA #AI #Agilex5.

0

0

5

RT @sundancedsp_inc: 🚀 Just published: “Understanding FPGA Boot Sequence”.How Ultrascale FPGAs boot up? This guide the process from reset t….

linkedin.com

🚀 Sundance just published: “Understanding the FPGA Boot Sequence: A Deep Dive into Ultrascale Architecture” Are you wondering how Ultrascale FPGAs boot? 🤔 If yes, this is a must-read for engineers...

0

3

0

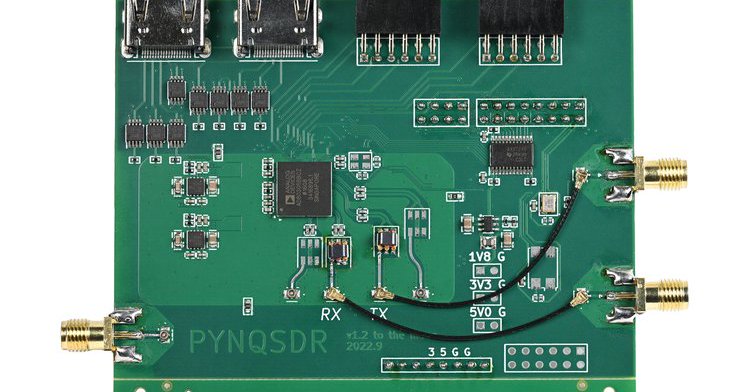

RT @regymm0: Thanks @crowd_supply for the support, my PYNQSDR HAT, a AD936X SDR extension card for the PYNQ-Z1 board, is now at pre-launch!….

crowdsupply.com

Add an SDR to the PYNQ-Z1 development board

0

7

0

RT @ATaylorFPGA: FPGAs excel at image processing applications. I have just released a white paper which talks all about image processing wi….

0

24

0

RT @enjoy_digital: 🚀 White Rabbit support for the LiteX M2 SDR is shaping up nicely!. First lock of the LiteX M2 SDR design as a WR Slave t….

0

19

0

RT @fpgahelper: It's not too late to back the @Terasic_FPGA Atum A3 Nano campaign on @crowd_supply . The latest update has links to the rec….

0

5

0

Feel free to read the Dissertaton:.

scholarsarchive.byu.edu

Field-Programmable Gate Arrays (FPGAs) leveraging soft processors, particularly those implementing the open-standard RISC-V Instruction Set Architecture (ISA), are increasingly important for space...

My PhD defense is scheduled! I’ll be presenting my work on fault-tolerant FPGA soft processor SoCs. Message me if you want a virtual invite.

0

6

65

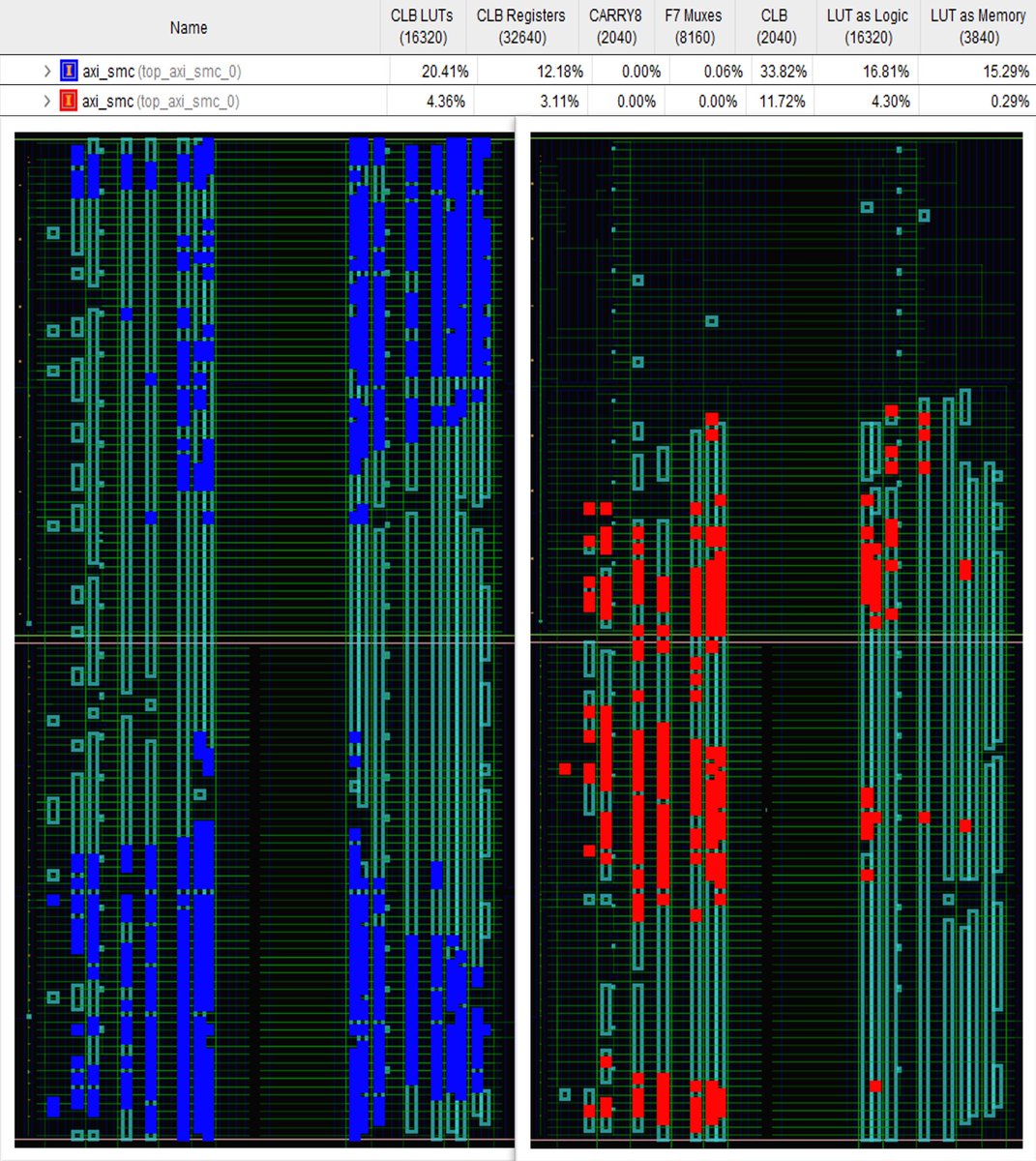

I passed! .Here are my slides:.

github.com

PhD Disseration Appendix for fault anlaysis of TMR soft RISC-V LiteX SoCs - AEW2015/phd-tmr-fault-analysis

My PhD defense is scheduled! I’ll be presenting my work on fault-tolerant FPGA soft processor SoCs. Message me if you want a virtual invite.

20

11

195