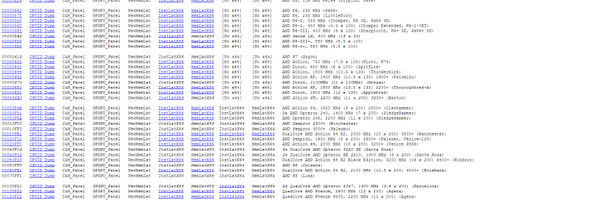

InstLatX64

@InstLatX64

Followers

4K

Following

583

Media

2K

Statuses

3K

x86/x64, SIMD, #AVX512, "Aha!" moments. I have been writing code since 1986.

Budapest, Europe

Joined August 2014

My future posts will be published there first, and here only later

4

0

32

It seems, #AMD utilizes their #Zen5 #FireRange CPUs in the embedded server space too #EPYC9005 - #SP5

#EPYC8005 - #SP6

#EPYC4005 - #AM5

#EPYC2005 - #FL1

https://t.co/eod4E89G2B

New #AMD CPUIDs: #Chagall ( #Zen3 #Threadripper) A00F82 [1] #GenoaX (1+GB L3 #Zen4 EPYC) A10F12 [2] #ShimadaPeak ( #Zen5 Threadripper) B00F8x [3] New #AMD codenames: #Grado (Zen5 #EPYC 4005) [5] #Medusa ( #Zen6 mobile, FP10) [5] GitHub: https://t.co/mSFyTusB8I 1/2

0

0

3

#Intel #VPMM is back in the 7th edition of "Intel® TDX Module Base Architecture Specification (What Changed)". Probably just a documentation bug. https://t.co/x0YvnFn7z3

What is #Intel #VPMM (Vector Extension Packed Matrix Multiplication)? CPUID.24h.ECX=1.ECX[0] From the latest TDX 1.5 specification (348549-006US pdf), page 116. https://t.co/f7opX6IQTa

1

2

7

#Intel #VPMM is back in the 7th edition of "Intel® TDX Module Base Architecture Specification (What Changed)". Probably just a documentation bug. https://t.co/x0YvnFn7z3

What is #Intel #VPMM (Vector Extension Packed Matrix Multiplication)? CPUID.24h.ECX=1.ECX[0] From the latest TDX 1.5 specification (348549-006US pdf), page 116. https://t.co/f7opX6IQTa

0

0

7

#Intel refreshed the "Intel Virtualization Technology for Directed I/O Architecture Specification" pdf to 5.1 https://t.co/5ORN4X3zBc

#Intel refreshed the "Intel Virtualization Technology for Directed I/O Architecture Specification" pdf to 5.0: https://t.co/8L4xKqoBRQ

0

1

12

..and the favorite VPTERNLOG[B,W] - how useful would be this! e.g. byte granularity, single-uop (mask)?0:(c?a:b) Source: https://t.co/VQNbSAcWOj 3/3 Who knows, perhaps they will resurrect in one of #AVX10.N...

0

0

5

#AVX512BITALG2 completes these useful instructions: VPLZCNT[B,W] - the missing byte & word LZCNT VPTZCNT[B,W,D,Q] - Analogous to LZCNT[B,W,D,Q] VPADD[,U]S[D,Q] - saturated signed / unsigned addition for dword / qword (but why there isn't VPSUB[,U]S[D,Q]?) 2/3

1

0

7

I found out a few days ago: At least 3 #AVX512 levels were planned, but they never released: #AVX512QVNNI - byte form of 4VNNIW, it would extinct with KNM/MIC; #AVX512DFMA - VDF[,n]MADD[P,S][S,D]; #AVX512BITALG2 - this is the most interesting for me; 1/3

1

1

16

What happened to the SiSoftware Sandra? Why hasn't a new one been released since October 2023? https://t.co/GNlvmX7Qrr

1

0

5

Is the TR somehow related to the Verona or Murano codenames? https://t.co/ngHUVdJa0H

0

0

3

The #Zen6-based #AMD #Threadripper is missing from this chart. I don't recall seeing its codename, does it even exist?

1

1

21

#AMD refreshed the "Revision Guide for AMD Family 19h Models A0h-AFh Processors" 57926 to v1.05 pdf (#Bergamo #Zen4c A0 CPUID AA0F02 #EPYC) https://t.co/7awi2wmiSL

0

0

11

GNR-WS 🤔 678X : 2.40GHz 192M 676X : 2.80GHz 144M 674X : 3.00GHz 144M 658X : 3.00GHz 144M 656 : 2.90GHz 72M 654 : 3.10GHz 72M 638 : 3.20GHz 72M 636 : 3.50GHz 48M 634 : 2.70GHz 48M

4

12

39

Granite Rapids Workstation! Xeon 600 Series

[GB6 CPU] Unknown CPU CPU: Intel Xeon 654 (18C 36T) Min/Max/Avg: 2983/4776/4730 MHz CPUID: A06D1 (GenuineIntel) Single: 2634 Multi: 14743 https://t.co/5bsbWVaLKx

0

4

39

I think #APX has bright future ahead of it. Not a clear commitment, but a very good sign: it appeared in Mark Papermaster's presentation along with "ACE" which seems to be a relabeled #AMX

#OCP2025 #AMD #x86EAG #Zen7

https://t.co/X2roicnCvm

https://t.co/58VpCSkeYS thx, @ravigiri!

@InstLatX64 @FelixCLC_ @LeslieB82382206 @philparkbot Update on the progress of the x86 advisory group from the @AMD keynote by Mark Papermaster at #OCP2025 - AMX becomes ACE?

1

7

70

#Intel released the 60th edition of the ISA Extensions Reference with official announcement of #AVX10 and #APX support on #NovaLake and FP8 type clarifications. Download: https://t.co/Q9tRje4Xfq

#DiamondRapids #NovaLake #WildcatLake #PantherCove #CoyoteCove #ArcticWolf

#Intel re-released the 59th edition of the ISA Extensions Reference with #USER_MSR clarifications: Download: https://t.co/cLv6PueAEY

#DiamondRapids #NovaLake #WildcatLake

#PantherCove #CoyoteCove #ArcticWolfs

9

23

93

#AMD #Zen6 znver6 ISA: - #AVX512_BMM (CPUID.80000021.EAX[23], VBMACOR16x16x16, VBMACXOR16x16x16, VBITREV) - #AVX512_FP16 - #AVX_NE_CONVERT - #AVX_IFMA - #AVX_VNNI_INT8 Source: https://t.co/hmQSDXlHpD

#AMD CPUID refresh: -- CPUID B80F00 is #Zen6 [1] -- #Zen5c #Sorano CPUID is B10F00 (#EPYC 8005, SP6 socket) [2],[3] -- #Zen5 #Grado CPUID is B40F40 (EPYC 4005, AM5 socket) [4] GitHub: https://t.co/R49g6q19qx 1/2

1

15

83

Sources: [1]: https://t.co/NZ8DxdGfsS [2]: https://t.co/WJXatdsm2f [3]: https://t.co/39bZxuLUGE [4]: https://t.co/PjkqfSXNw2 2/2

0

0

2

#AMD CPUID refresh: -- CPUID B80F00 is #Zen6 [1] -- #Zen5c #Sorano CPUID is B10F00 (#EPYC 8005, SP6 socket) [2],[3] -- #Zen5 #Grado CPUID is B40F40 (EPYC 4005, AM5 socket) [4] GitHub: https://t.co/R49g6q19qx 1/2

New #AMD CPUID dump: 64-Core #ThreadripperPro 9985WX (#ShimadaPeak, #Zen5) B00F81 GitHub: https://t.co/oGQfXqs32d

1

4

20